# 3.3 VOLT TIME SLOT INTERCHANGE DIGITAL SWITCH 4,096 x 4,096

IDT72V70840

#### **FEATURES:**

- · 32 serial input and output streams

- 4,096 x 4,096 channel non-blocking switching at 8.192 Mb/s

- Accepts data streams at 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s

- Per-channel Variable Delay Mode for low-latency applications

- Per-channel Constant Delay Mode for frame integrity applications

- Automatic identification of ST-BUS® and GCI serial streams

- Automatic frame offset delay measurement

- Per-stream frame delay offset programming

- · Per-channel high impedance output control

- Per-channel processor mode to allow microprocessor writes to TX streams

- Direct microprocessor access to all internal memories

- · Memory block programming for quick set-up

- IEEE-1149.1 (JTAG) Test Port

- Internal Loopback for testing

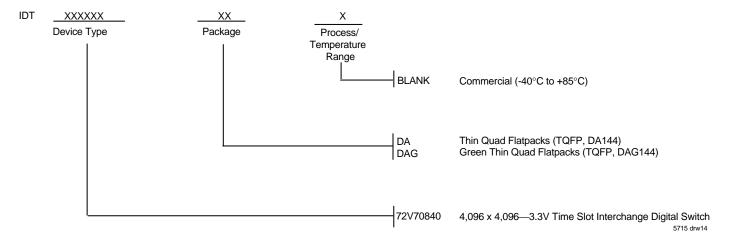

- Available in 144-pin Thin Quad Flatpack (TQFP) and 144-pin Ball Grid Array (BGA) packages

- Operating Temperature Range -40°C to +85°C

- 3.3V I/O with 5V tolerant inputs and TTL compatible outputs

#### **DESCRIPTION:**

The IDT72V70840 has a non-blocking switch capacity of 1,024 x 1,024 channels at 2.048 Mb/s, 2,048 x 2,048 channels at 4.096 Mb/s, and 4,096 x 4,096 channels at 8.192 Mb/s. With 32 inputs and 32 outputs, programmable per stream control, and a variety of operating modes the IDT72V70840 is designed for the TDM time slot interchange function in either voice or data applications.

Some of the main features of the IDT72V70840 are low power 3.3 Volt operation, automatic ST-BUS\*/GCI sensing, memory block programming, simple microprocessor interface, one cycle direct internal memory accesses,

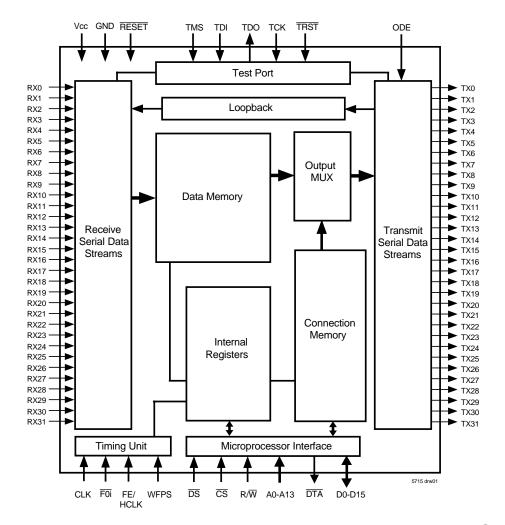

## **FUNCTIONAL BLOCK DIAGRAM**

October 2008

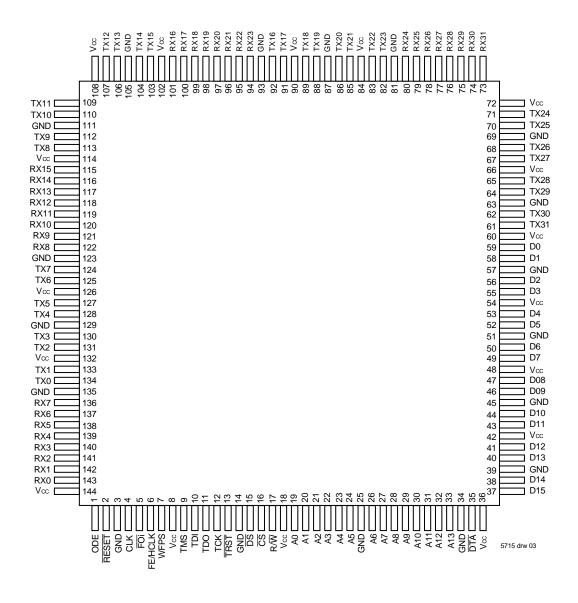

#### **PIN CONFIGURATIONS**

#### NOTE:

1. All I/O pins are 5V tolerant except for TMS, TDI and  $\overline{\text{TRST}}$ .

TQFP: 0.50mm pitch, 20mm x 20mm (DA144, order code: DA; DAG 144, order code: DAG)

TOP VIEW

## **PIN DESCRIPTION**

| SYMBOL  | NAME                                       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|--------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND     | Ground.                                    |     | Ground Rail.                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vcc     | Vcc                                        |     | +3.3 Volt Power Supply.                                                                                                                                                                                                                                                                                                                                                                                       |

| TX0-31  | TX Output 0 to 31<br>(Three-state Outputs) | 0   | Serial data output stream. These streams may have a data rate of 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s.                                                                                                                                                                                                                                                                                                        |

| RX0-31  | RX Input 0 to 31                           | - 1 | Serial data input stream. These streams may have a data rate of 2.048 Mb/s, 4.096 Mb/s or 8.192 Mb/s.                                                                                                                                                                                                                                                                                                         |

| F0i     | Frame Pulse                                | Ι   | This input accepts and automatically identifies frame synchronization signals formatted according to ST-BUS® and GCI specifications.                                                                                                                                                                                                                                                                          |

| FE/HCLK | Frame Evaluation/<br>HCLK Clock            | Ι   | When LOW, this pin is the frame measurement input. When HIGH, the HCLK (4.096 MHZ clock) is required for frame alignment in the wide frame pulse (WFP) mode. There is no internal pull-up or pull-down. If this pin is unused, an external pull-up or pull-down must be provided.                                                                                                                             |

| CLK     | Clock                                      | Ι   | Serial clock for shifting data in/out on the serial streams (RX/TX 0-31). This input accepts a 4.096 MHz clock when data streams @ 2.048 Mb/s, a 8.192 MHz clock when data streams @ 4.096 Mb/s, a 16.384 MHz clock when data streams @ 8.192 Mb/s.                                                                                                                                                           |

| TMS     | Test Mode Select                           | I   | JTAG signal that controls the state transitions of the TAP controller. This pin is pulled HIGH by an internal pull-up when not driven.                                                                                                                                                                                                                                                                        |

| TDI     | Test Serial Data In                        | Ι   | JTAG serial test instructions and data are shifted in on this pin. This pin is pulled HIGH by an internal pull-up when not driven.                                                                                                                                                                                                                                                                            |

| TDO     | Test Serial Data Out                       | 0   | JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high-impedance state when JTAG scan is not enabled.                                                                                                                                                                                                                                                                    |

| TCK     | Test Clock                                 | - 1 | Provides the clock to the JTAG test logic.                                                                                                                                                                                                                                                                                                                                                                    |

| TRST    | Test Reset                                 | -   | Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-reset state. This pin is pulled by an internal pull-up when not driven. This pin should be pulsed LOW on power-up, or held LOW, to ensure that the IDT72V70840 is in the normal functional mode.                                                                                                                           |

| RESET   | Device Reset<br>(Schmitt Trigger Input)    | _   | This input (active LOW) puts the IDT72V70840 in its reset state that clears the device internal counters, registers and brings TX0-31 and microport data outputs to a high-impedance state. The time constant for a power up reset circuit must be a minimum of five times the rise time of the power supply. In normal operation, the RESET pin must be held LOW for a minimum of 100ns to reset the device. |

| WFPS    | Wide Frame Pulse Select                    | _   | When 1, enables the wide frame pulse (SFP) Frame Alignment interface. When 0, the device operates in ST-BUS® /GCI mode.                                                                                                                                                                                                                                                                                       |

| DS      | Data Strobe                                | - 1 | This active LOW input works in conjunction with $\overline{\text{CS}}$ to enable the read and write operations.                                                                                                                                                                                                                                                                                               |

| R/W     | Read/Write                                 | - 1 | This input controls the direction of the data bus lines during a microprocessor access.                                                                                                                                                                                                                                                                                                                       |

| CS      | Chip Select                                | I   | Active LOW input used by a microprocessor to activate the microprocessor port of IDT72V70840.                                                                                                                                                                                                                                                                                                                 |

| A0-13   | Address Bus 0 to 13                        | I   | These pins allow direct access to Connection Memory, Data Memory and internal control registers.                                                                                                                                                                                                                                                                                                              |

| D0-15   | Data Bus 0-15                              | I/O | These pins are the data bits of the microprocessor port.                                                                                                                                                                                                                                                                                                                                                      |

| DTA     | Data Transfer<br>Acknowledgment            | 0   | This active LOW signal indicates that a data bus transfer is complete. When the bus cycle ends, this pin drives HIGH and then goes high-impedance, allowing for faster bus cycles with a weaker pull-up resistor. A pull-up resistor is required to hold a HIGH level when the pin is in high-impedance.                                                                                                      |

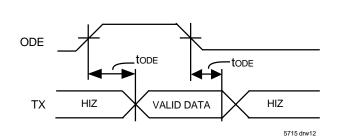

| ODE     | Output Drive Enable                        | Ι   | This is the output enable control for the TX0-31 serial outputs. When ODE input is LOW and the OSB bit of the CR register is LOW, TX0-31 are in a high-impedance state. If this input is HIGH, the TX0-31 output drivers are enabled. However, each channel may still be put into a high-impedance state by using the per channel control bit in the connection memory.                                       |

### **DECRIPTION (CONTINUED)**

$\label{lem:JTAG} JTAG \ Test \ Access \ Port \ (TAP) \ and \ per \ stream \ programmable \ input \ offset \ delay, \\ variable \ or \ constant \ throughput \ modes, \ internal \ loopback, \ output \ enable, \ and \ Processor \ Mode.$

The 32 serial input streams (RX) of the IDT72V70840 can be run up to  $8.192\,\text{Mb/s}$  allowing  $128\,\text{channels}$  per  $125\,\mu\text{s}$  frame. The data rates on the output streams (TX) are identical to those on the input stream.

With two main operating modes, Processor Mode and Connection Mode, the IDT72V70840 can easily switch data from incoming serial streams (Data Memory) or from the controlling microprocessor (Connection Memory). As control and status information is critical in data transmission, the Processor Mode is especially useful when there are multiple devices sharing the input and output streams.

With data coming from multiple sources and through different paths, data entering the device is often delayed. To handle this problem, the IDT72V70840 has a frame evaluation feature to allow individual streams to be offset from the frame pulse in half clock-cycle intervals up to +4.5 clock cycles.

The IDT72V70840 also provides a JTAG test access port, an internal loopback feature, memory block programming, a simple microprocessor interface and automatic ST-BUS\*/GCI sensing to shorten setup time, aid in debugging and ease use of the device without sacrificing capabilities.

#### **FUNCTIONAL DESCRIPTION**

#### **DATA AND CONNECTION MEMORY**

All data that comes in through the RX inputs go through a serial-to-parallel conversion before being stored into internal Data Memory. The 8 KHz frame pulse ( $\overline{\text{F0i}}$ ) is used to mark the 125 $\mu$ s frame boundaries and to sequentially address the input channels in Data Memory.

Data output on the TX streams may come from either the Serial Input Streams (Data Memory) or from the microprocessor (Connection Memory). In the case that RX input data is to be output, the addresses in connection memory are used to specify a stream and channel of the input. The connection memory is setup in such a way that each location corresponds to an output channel for each particular stream. In that way, more than one channel can output the same data.

In Processor Mode, the microprocessor writes data to the connection memory locations corresponding to the stream and channel that is to be output. The lower half (8 least significant bits) of the connection memory is output every frame until the microprocessor changes the data or mode of the channel. By using this Processor Mode capability, the microprocessor can access input and output time-slots on a per channel basis.

The four most significant bits of the connection memory are used to control per channel functions of the out put streams. Specifically, there are bits for Processor or Connection mode, Constant or Variable delay, enables or disables of output drivers, and controls for the Loopback function.

If the per channel OE is set to zero, only that particular channel (8-bits) will be in the high-impedance state. If however, the ODE input pin is low or the Output Standby Bit (OSB) in the Control Register is low, all of the outputs will be in a high-impedance state even if a particular channel in connection memory has enabled the output for that channel. In other words, the ODE pin and OSB control bit are master output enables for the device (Table 3).

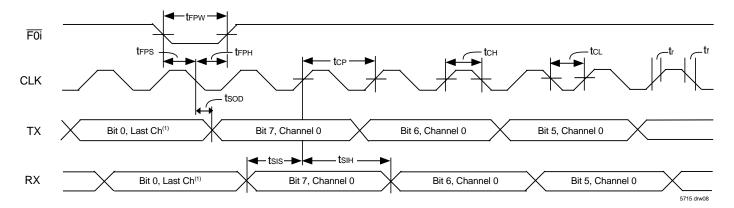

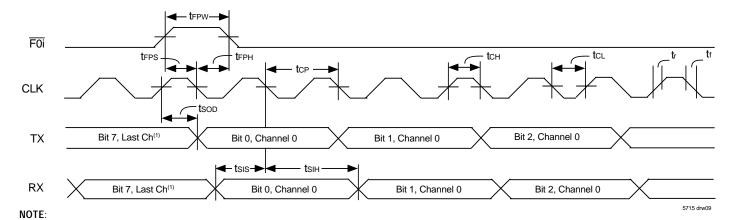

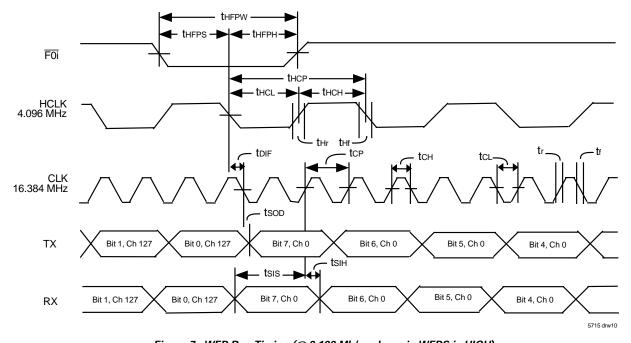

#### **SERIAL DATA INTERFACE TIMING**

The master clock frequency must always be twice the data rate, e.g. for a serial data rates of 2.048 Mb/s, the master clock (CLK) must be at 4.096 MHz. The input and output stream data rates will always be identical. See control register bits DR1-0 description (Table 5) for data and clock rate selections.

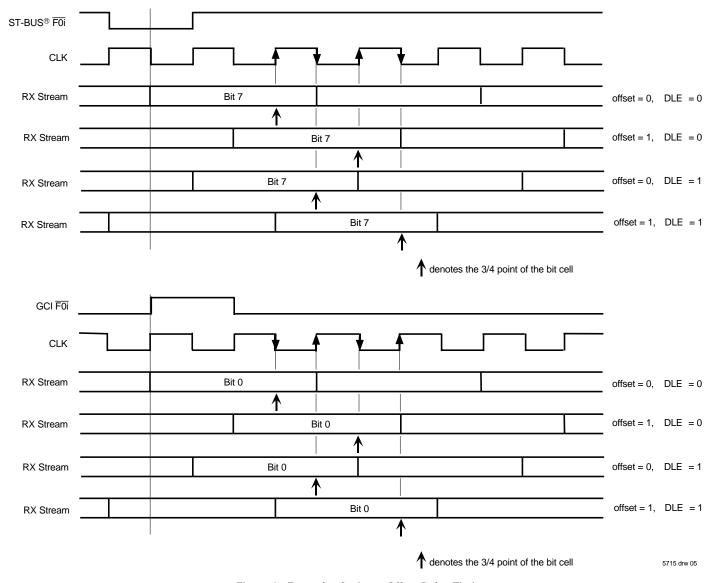

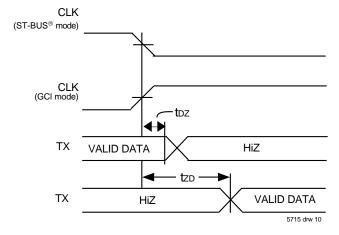

The IDT72V70840 provides two different interface timing modes, ST-BUS® or GCI. The IDT72V70840 automatically detects the presence of an input frame pulse and identifies it as either ST-BUS® or GCI. In ST-BUS® format, every second falling edge of the master clock marks a bit boundary and the data is clocked in on the rising edge of CLK, three quarters of the way into the bit cell. In GCI format, every second rising edge of the master clock marks the bit boundary and data is clocked in on the falling edge of CLK at three quarters of the way into the bit cell.

#### INPUT FRAME OFFSET SELECTION

Input frame offset selection allows the channel alignment of individual input streams to be offset with respect to the output stream channel alignment (i.e.  $\overline{\text{Foi}}$ ). Although all input data comes in at the same speed, delays can be caused by variable path serial backplanes and variable path lengths which may be implemented in large centralized and distributed switching systems. Because data is often delayed this feature is useful in compensating for the skew between clocks.

Each input stream can have its own delay offset value by programming the frame input offset registers (FOR, Table 8). The maximum allowable skew is +4 master clock (CLK) periods forward with a resolution of 1/2 clock period. The output frame offset cannot be offset or adjusted.

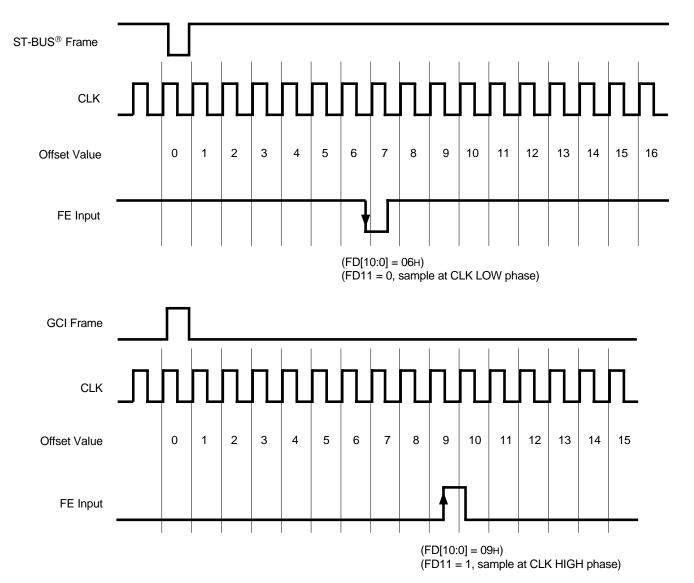

#### SERIAL INPUT FRAME ALIGNMENT EVALUATION

The IDT72V70840 provides the frame evaluation (FE) input to determine different data input delays with respect to the frame pulse F0i.

A measurement cycle is started by setting the start frame evaluation (SFE) bit lowfor at least one frame. When the SFE bit in the Control Register is changed from low to high, the evaluation starts. Two frames later, the complete frame evaluation (CFE) bit of the frame alignment register (FAR) changes from low to high to signal that a valid offset measurement is ready to be read from bits 0 to 11 of the FAR register. The SFE bit must be set to zero before a new measurement cycle is started.

In ST-BUS® mode, the falling edge of the frame measurement signal (FE) is evaluated against the falling edge of the ST-BUS® frame pulse. In GCI mode, the rising edge of FE is evaluated against the rising edge of the GCI frame pulse. See Table 7 and Figure 1 for the description of the frame alignment register.

#### MEMORY BLOCK PROGRAMMING

The IDT72V70840 provides users with the capability of initializing the entire connection memory block in two frames. To set bits 12 to 15 of every connection memory location, first program the desired pattern in bits 5 to 8 of the Control Register.

The block programming mode is enabled by setting the memory block program (MBP) bit of the control register high. When the block programming enable (BPE) bit of the Control Register is set to high, the block programming data will be loaded into the bits 12 to 15 of every connection memory location. The other connection memory bits (bit 0 to bit 11) are loaded with zeros. When the memory block programming is complete, the device resets the BPE bit to zero.

#### LOOPBACK CONTROL

The loopback control (LPBK) bit of each connection memory location allows the TX output data to be looped backed internally to the RX input for diagnostic purposes.

If the LPBK bit is high, the associated TX output channel data is internally looped back to the RX input channel (i.e., data from TXn channel m routes to the RXn channel m internally); if the LPBK bit is low, the loopback feature is disabled. For proper per-channel loopback operation, the contents of frame delay offset registers must be set to zero.

#### **DELAY THROUGH THE IDT72V70840**

The switching of information from the input serial streams to the output serial streams results in a throughput delay. The device can be programmed to perform time-slot interchange functions with different throughput delay capabilities on a per-channel basis. For voice applications, variable throughput delay is best as it ensure minimum delay between input and output data. In wideband data applications, constant throughput delay is best as the frame integrity of the information is maintained through the switch.

The delay through the device varies according to the type of throughput delay selected in the  $\overline{V}/C$  bit of the connection memory.

#### VARIABLE DELAY MODE ( $\overline{V}/C$ BIT = 0)

In this mode, the delay is dependent only on the combination of source and destination channels and is independent of input and output streams. The minimum delay achievable in the IDT72V70840 is three time-slots. If the input channel data is switched to the same output channel (channel n, frame p), it will be output in the following frame (channel n, frame p+1). The same is true if the input channel n is switched to output channel n+1 or n+2. If the input channel n is switched to output channel n+3, n+4,..., the new output data will appear in the same frame. Table 2 shows the possible delays for the IDT72V70840 in the variable delay mode.

#### CONSTANT DELAY MODE ( $\overline{V}/C$ BIT = 1)

In this mode, frame integrity is maintained in all switching configurations by making use of a multiple data memory buffer. Input channel data is written into the data memory buffers during frame n will be read out during frame n+2. In the IDT72V70840, the minimum throughput delay achievable in the constant delay mode will be one frame. For example, when input time-slot 31 is switched to output time-slot 0. The maximum delay of 94 time-slots of delay occurs when time-slot 0 in a frame is switched to time-slot 31 in the frame.

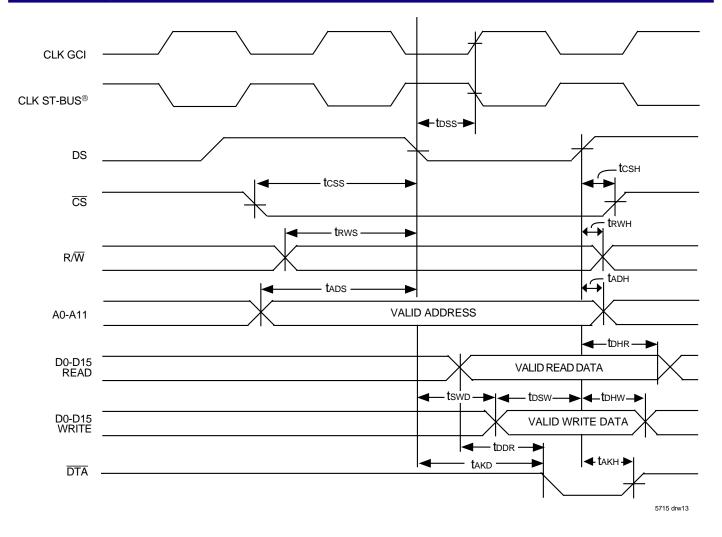

#### MICROPROCESSOR INTERFACE

The IDT72V70840's microprocessor interface looks like a standard RAM interface to improve integration into a system. With a 12-bit address bus and a 16-bit data bus, read and writes are mapped directly into Data and Connection memories and require only one cycle to access. By allowing the internal memories to be randomly accessed in one cycle, the controlling microprocessor has more time to manage other peripheral devices and can more easily and quickly gather information and setup the switch paths.

Table 4 shows the mapping of the addresses into internal memory blocks and Table 5 shows the Control Register information.

#### **MEMORY MAPPING**

The address bus on the microprocessor interface selects the internal registers and memories of the IDT72V70840.

The two most significant bits of the address select between the registers, Data Memory, and Connection Memory. If A13 and A12 are HIGH, A11-A0 are used to address the Data Memory. If A13 is HIGH and A12 is LOW, A11-A0 are used to address Connection Memory. If A13 is LOW and A12 is HIGH A11-A0 are used to select the Control Register, Frame Alignment Register, and Frame Offset Registers. See Table 4 for mappings.

As explained in the Serial Data Interface Timing and Switching Configurations sections, after system power-up, the Control Register should be programmed immediately to establish the desired switching configuration.

The data in the Control Register consists of the Memory Block Programming bit (MBP), the Block Programming Data (BPE) bits, the Begin Block Programming Enable (BPE), the Output Stand By, Start Frame Evaluation, and Data Rate Select bits. As explained in the Memory Block Programming section, the BPE begins the programming if the MBP bit is enabled. This allows the entire connection memory block to be programmed with the Block Programming Data bits. If the ODE pin is low, the OSB bit enables (if high) or disables (if low) all TX output drivers. If the ODE pin is high, the contents of the OSB bit is ignored and all TX output drivers are enabled.

#### CONNECTION MEMORY CONTROL

If the ODE pin or the OSB bit is high, the OE bit of each connection memory location controls the output drivers-enables (if high) or disables (if low). See Table 3 for detail.

The Processor Channel (PC) bit of the Connection Memory selects between Processor Mode and Connection Mode. If high, the contents of the Connection Memory are output on the TX streams. If low, the Stream Address Bit (SAB) and the Channel Address Bit (CAB) of the Connection Memory defines the source information (stream and channel) of the time-slot that will be switched to the output from Data Memory.

Also in the Connection Memory is the  $\overline{V}/C$  (Variable/Constant Delay) bit. Each Connection Memory location allows the per-channel selection between variable and constant throughput delay modes.

If the LPBK bit is high, the associated TX output channel data is internally looped back to the RX input channel (i.e., RXn channel m data comes from the TXn channel m). If the LPBK bit is low, the loopback feature is disabled. For proper per-channel loopback operation, the contents of the frame delay offset registers must be set to zero.

#### INITIALIZATION OF THE IDT72V70840

After power up, the state of the connection memory is unknown. As such, the outputs should be put in high impedance by holding the ODE low. While the ODE is low, the microprocessor can initialize the device, program the active paths, and disable unused outputs by programming the OE bit in connection memory. Once the device is configured, the ODE pin (or OSB bit depending on initialization) can be switched.

## TABLE 1 — CONSTANT THROUGHPUT DELAY VALUE

| Input Rate | Delay for Constant Throughput Delay Mode<br>(m – output channel number)<br>(n – input channel number) |

|------------|-------------------------------------------------------------------------------------------------------|

| 2.048 Mb/s | 32 + (32 – n) +m time-slots                                                                           |

| 4.096 Mb/s | 64 + (64 – n) +m time-slots                                                                           |

| 8.192 Mb/s | 128 + (128 – n) +m time-slots                                                                         |

#### **TABLE 2 — VARIABLE THROUGHPUT DELAY VALUE**

| IADEL IA   | IIIIADEE IIIIIVOOTIII C | ,, belai valve                               |                  |

|------------|-------------------------|----------------------------------------------|------------------|

|            |                         | Delay for Variable Throughput Delay Mode     |                  |

| Input Rate | (m –                    | output channel number; n - input channel nur | nber)            |

|            | m < n                   | m = n, n+1, n+2                              | m > n+2          |

| 2.048 Mb/s | 32 – (n-m) time-slots   | (m-n + 32) time-slots                        | (m-n) time-slots |

| 4.096 Mb/s | 64 – (n-m) time-slots   | (m-n+64) time-slots                          | (m-n) time-slots |

| 8.192 Mb/s | 128 – (n-m) time-slots  | (m-n+128) time-slots                         | (m-n) time-slots |

### **TABLE 3 — OUTPUT HIGH IMPEDANCE CONTROL**

| OE bit in Connection<br>Memory | ODE pin    | OSB bit in CR<br>Register | TX Stream Output<br>Status    |

|--------------------------------|------------|---------------------------|-------------------------------|

| 0                              | Don't Care | Don't Care                | Per Channel<br>High-Impedance |

| 1                              | 0          | 0                         | High-Impedance                |

| 1                              | 0          | 1                         | Enable                        |

| 1                              | 1          | 0                         | Enable                        |

| 1                              | 1          | 1                         | Enable                        |

### **TABLE 4 — INTERNAL REGISTER AND ADDRESS MEMORY MAPPING**

| A13 | A12 | A11  | A10  | A9   | A8   | A7   | A6  | <b>A</b> 5 | A4  | A3  | A2  | A1  | A0  | R/W | Location             |

|-----|-----|------|------|------|------|------|-----|------------|-----|-----|-----|-----|-----|-----|----------------------|

| 1   | 1   | STA4 | STA3 | STA2 | STA1 | STA0 | CH6 | CH5        | CH4 | CH3 | CH2 | CH1 | CH0 | R   | Data Memory          |

| 1   | 0   | STA4 | STA3 | STA2 | STA1 | STA0 | CH6 | CH5        | CH4 | CH3 | CH2 | CH1 | CH0 | R/W | Connect. Memory      |

| 0   | 1   | 0    | 0    | 0    | 0    | Х    | Х   | Х          | Х   | Х   | Х   | Х   | Х   | R/W | Control Register     |

| 0   | 1   | 0    | 0    | 0    | 1    | Х    | Х   | Х          | Х   | Х   | Х   | Х   | Х   | R/W | Frame Align Register |

| 0   | 1   | 0    | 0    | 1    | 0    | Х    | Х   | Х          | Х   | Х   | Х   | Х   | Х   | R/W | FOR0                 |

| 0   | 1   | 0    | 0    | 1    | 1    | Х    | Х   | Х          | Х   | Х   | Х   | Х   | Х   | R/W | FOR1                 |

| 0   | 1   | 0    | 1    | 0    | 0    | Х    | Х   | Х          | Х   | Х   | Х   | Х   | Х   | R/W | FOR2                 |

| 0   | 1   | 0    | 1    | 0    | 1    | Х    | Х   | Х          | Х   | Х   | Х   | Х   | Х   | R/W | FOR3                 |

| 0   | 1   | 0    | 1    | 1    | 0    | Х    | Х   | Х          | Х   | Х   | х   | Х   | Х   | R/W | FOR4                 |

| 0   | 1   | 0    | 1    | 1    | 1    | Х    | Х   | Х          | Х   | Х   | х   | Х   | Х   | R/W | FOR5                 |

| 0   | 1   | 1    | 0    | 0    | 0    | Х    | Х   | Х          | Х   | Х   | Х   | Х   | Х   | R/W | FOR6                 |

| 0   | 1   | 1    | 0    | 0    | 1    | Х    | Х   | Х          | Х   | Х   | Х   | Х   | Х   | R/W | FOR7                 |

## TABLE 5 — CONTROL REGISTER (CR) BITS

| Reset Va | alue: 0000н.                               |                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |                                                                                                  |                                                                                                                                                      |  |  |  |  |  |  |

|----------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 15       | 14 13 12                                   | 11 10 9                                                                                                                                                                                                                                                                                                                                                                | 8 7 6                                                              | 5 4 3 2                                                                                          | 2 1 0                                                                                                                                                |  |  |  |  |  |  |

| 0        | 0 0 0                                      | 0 0 MBP                                                                                                                                                                                                                                                                                                                                                                | BPD3 BPD2 BPD1 B                                                   | PD0 BPE OSB SF                                                                                   | E DR1 DR0                                                                                                                                            |  |  |  |  |  |  |

| Bit      | Name                                       | Description                                                                                                                                                                                                                                                                                                                                                            | Description                                                        |                                                                                                  |                                                                                                                                                      |  |  |  |  |  |  |

| 15-10    | Unused                                     | Must be zero for normal op                                                                                                                                                                                                                                                                                                                                             | eration.                                                           |                                                                                                  |                                                                                                                                                      |  |  |  |  |  |  |

| 9        | MBP<br>(Memory Block Program)              | When 1, the connection mobit 11 to bit 15. When 0, this                                                                                                                                                                                                                                                                                                                |                                                                    | ure is ready for the programmii                                                                  | ng of Connection Memory high bits,                                                                                                                   |  |  |  |  |  |  |

| 8-5      | BPD3-0<br>(Block Programming Data)         | These bits carry the value to be loaded into the connection memory block whenever the memory block programming feature is activated. After the MBP bit in the control register is set to 1 and the BPE bit is set to 1, the contents of the bits BPD3-0 are loaded into bit 15 and 12 of the connection memory. Bit 11 to bit 0 of the connection memory are set to 0. |                                                                    |                                                                                                  |                                                                                                                                                      |  |  |  |  |  |  |

| 4        | BPE<br>(Begin Block<br>Programming Enable) | register have to be defined<br>complete the block prograt<br>operation is completed. V                                                                                                                                                                                                                                                                                 | d in the same write operation. C<br>mming. After the programming t | Once the BPE bit is set HIGH, if function has finished, the BPE IMBP can be set to 0 to abort to | e BPE and BPD4-0 bits in the CR the device requires two frames to bit returns to zero to indicate the ensure proper operation. When roper operation. |  |  |  |  |  |  |

| 3        | OSB<br>(Output Stand By)                   |                                                                                                                                                                                                                                                                                                                                                                        | = 0, the output drivers of TX0 t<br>TX31 function normally. When   |                                                                                                  | e mode. When ODE = 0 and OSB = 1, drivers function normally.                                                                                         |  |  |  |  |  |  |

| 2        | SFE<br>(Start Frame Evaluation)            |                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |                                                                                                  | bit in the FAR register changes from this bit to zero for at least one frame.                                                                        |  |  |  |  |  |  |

| 1-0      | DR1-0                                      | DR1                                                                                                                                                                                                                                                                                                                                                                    | DR0                                                                | Data Rate                                                                                        | Master Clock                                                                                                                                         |  |  |  |  |  |  |

|          | (Data Rate Select)                         | 0                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                  | 2.048 Mb/s                                                                                       | 4.096 MHz                                                                                                                                            |  |  |  |  |  |  |

|          |                                            | 0                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                  | 4.096 Mb/s                                                                                       | 8.192 MHz                                                                                                                                            |  |  |  |  |  |  |

|          |                                            | 1                                                                                                                                                                                                                                                                                                                                                                      | 0<br>1                                                             | 8.192 Mb/s<br>Reserved                                                                           | 16.384 MHz<br>Reserved                                                                                                                               |  |  |  |  |  |  |

## **TABLE 6 — CONNECTION MEMORY BITS**

| 15<br>LPB | K V/C PC OE                                 | 11 10 9 8 7 6 5 4 3 2 1 0  SAB4 SAB3 SAB2 SAB1 SAB0 CAB6 CAB5 CAB4 CAB3 CAB2 CAB1 CAB0                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|-----------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Bit       | Name                                        | Description                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 15        | LPBK<br>(Per Channel Loopback)              | When 1, the RX n channel m data comes from the TX n channel m. For proper per channel loopback operations, set the delay offset register bits OFn[2:0] to zero for the streams which are in the loopback mode.                                                                                         |  |  |  |  |  |  |  |  |

| 14        | √/C (Variable/Constant<br>Throughput Delay) | This bit is used to select between the variable (LOW) and constant delay (HIGH) mode on a per-channel basis.                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| 13        | PC<br>(Processor Channel)                   | When 1, the contents of the connection memory are output on the corresponding output channel and stream. Only the lower byte (bit 7 – bit 0) will be output to the TX output pins. When 0, the contents of the connection memory are the data memory address of the switched input channel and stream. |  |  |  |  |  |  |  |  |

| 12        | OE<br>(Output Enable)                       | This bit enables the TX output drivers on a per-channel basis. When 1, the output driver functions normally. When 0, the output driver is in a high-impedance state.                                                                                                                                   |  |  |  |  |  |  |  |  |

| 11-7      | SAB4-0 (Source Stream<br>Address Bits)      | The binary value is the number of the data stream for the source of the connection.                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| 6-0       | CAB6-0 (Source Channel Address Bits)        | Channel The binary value is the number of the channel for the source of the connection.                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

## **TABLE 7 — FRAME ALIGNMENT REGISTER (FAR) BITS**

| Re    | set Value:                                                  | 0000н.    |                                                                                                                                                                                                         |          |        |   |   |   |   |   |   |   |   |   |  |  |

|-------|-------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|---|---|---|---|---|---|---|---|---|--|--|

| 15    | 14 13                                                       | 12        | 11                                                                                                                                                                                                      | 10       | 9      | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| 0     | 0 0 0 CFE FD11 FD10 FD9 FD8 FD7 FD6 FD5 FD4 FD3 FD2 FD1 FD0 |           |                                                                                                                                                                                                         |          |        |   |   |   |   |   |   |   |   |   |  |  |

| Bit   | Name                                                        | Descript  | Description                                                                                                                                                                                             |          |        |   |   |   |   |   |   |   |   |   |  |  |

| 15-13 | Unused                                                      | Mustbez   | ero for no                                                                                                                                                                                              | rmal ope | ration |   |   |   |   |   |   |   |   |   |  |  |

| 12    | CFE (Complete Frame Evaluation)                             |           | When CFE = 1, the frame evaluation is completed and bits FD10 to FD0 bits contains a valid frame alignment offset. This bit is reset to zero, when SFE bit in the CR register is changed from 1 to 0.   |          |        |   |   |   |   |   |   |   |   |   |  |  |

| 11    | FD11<br>(Frame Delay Bit 11)                                |           | The falling edge of FE (or rising edge for GCI mode) is sampled during the CLK-high phase (FD11 = 1) or during the CLK-low phase (FD11 = 0). This bit allows the measurement resolution to ½ CLK cycle. |          |        |   |   |   |   |   |   |   |   |   |  |  |

| 10-0  | FD10-0                                                      | The binar | The binary value expressed in these bits refers to the measured input offset value. These bits are rest to zero when the SFE bit of the CR register changes from 1 to 0. (FD10 – MSB, FD0 – LSB)        |          |        |   |   |   |   |   |   |   |   |   |  |  |

Figure 1. Example for Frame Alignment Measurement

## TABLE 8 — FRAME INPUT OFFSET REGISTER (FOR) BITS

| Res                  | set Value         | 9:    | 0000н                | for all FO  | Rregister  | S.         |          |                            |            |             |             |       |       |       |                                  |                                |

|----------------------|-------------------|-------|----------------------|-------------|------------|------------|----------|----------------------------|------------|-------------|-------------|-------|-------|-------|----------------------------------|--------------------------------|

| 15                   | 14                | 13    | 12                   | 11          | 10         | 9          | 8        | 7                          | 6          | 5           | 4           | 3     | 2     | 1     | 0                                |                                |

| OF32                 | OF31              | OF30  | DLE3                 | OF22        | OF21       | OF20       | DLE2     | OF12                       | OF11       | OF10        | DLE1        | OF02  | OF01  | OF00  | DLE0                             |                                |

| 15                   | 14                | 13    | 12                   | 11          | 10         | 9          | 8        | FOR0 Reg                   | ister<br>6 | 5           | 4           | 3     | 2     | 1     | 0                                |                                |

| OF72                 | 0F71              | OF70  | DLE7                 | OF62        | OF61       | OF60       | DLE6     | OF52                       | OF51       | OF50        | DLE5        | OF42  | OF41  | OF40  | DLE4                             |                                |

|                      |                   |       | <u> </u>             | <u> </u>    |            |            |          | FOR1 Reg                   |            |             |             |       |       |       |                                  |                                |

| 15                   | 14                | 13    | 12                   | 11          | 10         | 9          | 8        | 7                          | 6          | 5           | 4           | 3     | 2     | 1     | 0                                | i                              |

| OF112                | OF111             | OF110 | DLE11                | OF102       | OF101      | OF100      | DLE10    | OF92                       | OF91       | OF90        | DLE9        | OF82  | OF81  | OF80  | DLE8                             |                                |

|                      |                   |       |                      |             |            |            |          | FOR2 Reg                   | jister     |             |             |       |       |       |                                  |                                |

| 15                   | 14                | 13    | 12                   | 11          | 10         | 9          | 8        | 7                          | 6          | 5           | 4           | 3     | 2     | 1     | 0                                | I                              |

| OF312                | OF311             | OF310 | DLE31                | OF142       | OF141      | OF140      | DLE14    | OF132                      | OF131      | OF130       | DLE13       | OF122 | OF121 | OF120 | DLE12                            |                                |

| 15                   | 14                | 13    | 12                   | 11          | 10         | 9          | 8<br>8   | FOR3 Reg                   | ister<br>6 | 5           | 4           | 3     | 2     | 1     | 0                                |                                |

| OF192                | OF191             | OF190 | DLE19                | OF182       | OF181      | OF180      | DLE18    | OF172                      | OF171      | OF170       | DLE17       | OD162 | OD161 | OF160 | DLE16                            |                                |

|                      |                   |       |                      |             |            |            |          | FOR4 Reg                   |            |             |             |       |       |       |                                  |                                |

| 15                   | 14                | 13    | 12                   | 11          | 10         | 9          | 8        | 7                          | 6          | 5           | 4           | 3     | 2     | 1     | 0                                |                                |

| OF232                | OF231             | OF230 | DLE23                | OF222       | OF221      | OF220      | DLE22    | OF212                      | OF211      | OF210       | DLE21       | OF202 | OF201 | OF200 | DLE20                            |                                |

| 15                   | 14                | 12    | 12                   | 11          | 10         | 0          |          | FOR5 Reg                   |            | -           | 4           | 2     | 2     | 1     | 0                                |                                |

| 15                   | 14                | 13    | 12                   | 11          | 10         | 9          | 8        | 7                          | 6          | 5           | 4           | 3     | 2     | 1     | 0                                |                                |

| OF272                | OF271             | OF270 | DLE27                | OF262       | OF261      | OF260      | DLE26    | OF252                      | OF251      | OF250       | DLE25       | OF242 | OF241 | OF240 | DLE24                            |                                |

| 15                   | 14                | 13    | 12                   | 11          | 10         | 9          | 8<br>8   | FOR6 Reg                   | ister<br>6 | 5           | 4           | 3     | 2     | 1     | 0                                |                                |

| OF312                | OF311             | OF310 | DLE31                | OF302       | OF301      | OF300      | DLE30    | OF292                      | OF291      | OF290       | DLE29       | OF282 | OF281 | OF280 | DLE28                            |                                |

|                      |                   |       |                      |             |            |            |          | FOR7 Reg                   | ister      |             |             |       |       |       |                                  |                                |

| Nan                  | ne <sup>(1)</sup> |       | Description          | nn          |            |            |          |                            |            |             |             |       |       |       |                                  |                                |

| OFn2, O<br>(Offset B | Fn1, OF           |       | These th<br>The inpu | ree bits de | set can be | selected   |          |                            |            |             |             |       |       |       | n: i.e., to sta<br>nal is applie | ort a new fram<br>d to the F0i |

| DLEn                 |                   |       | ST-BUS' (Data Lat    | ch Edge)    | DL         | En = 1, if | when clo | ng edge is<br>ck falling e | edge is at | the ¾ of th | ne bit cell | l.    |       |       |                                  |                                |

|                      |                   |       | GCI mod              | ie:         |            |            |          | ng edge is<br>ck rising e  |            |             |             |       |       |       |                                  |                                |

#### NOTE:

1. n denotes an input stream number from 0 to 31.

## TABLE 9 — OFFSET BITS (OFn2, OFn1, OFn0, DLEn) & FRAME DELAY BITS (FD11, FD2-0)

| Input Stream                    |      |     | nt Result from<br>Delay Bits |     | Corresponding<br>Offset Bits |      |      |      |  |

|---------------------------------|------|-----|------------------------------|-----|------------------------------|------|------|------|--|

| Offset                          | FD11 | FD2 | FD1                          | FD0 | OFn2                         | OFn1 | OFn0 | DLEn |  |

| No clock period shift (Default) | 1    | 0   | 0                            | 0   | 0                            | 0    | 0    | 0    |  |

| + 0.5 clock period shift        | 0    | 0   | 0                            | 0   | 0                            | 0    | 0    | 1    |  |

| + 1.0 clock period shift        | 1    | 0   | 0                            | 1   | 0                            | 0    | 1    | 0    |  |

| + 1.5 clock period shift        | 0    | 0   | 0                            | 1   | 0                            | 0    | 1    | 1    |  |

| + 2.0 clock period shift        | 1    | 0   | 1                            | 0   | 0                            | 1    | 0    | 0    |  |

| + 2.5 clock period shift        | 0    | 0   | 1                            | 0   | 0                            | 1    | 0    | 1    |  |

| + 3.0 clock period shift        | 1    | 0   | 1                            | 1   | 0                            | 1    | 1    | 0    |  |

| + 3.5 clock period shift        | 0    | 0   | 1                            | 1   | 0                            | 1    | 1    | 1    |  |

| + 4.0 clock period shift        | 1    | 1   | 0                            | 0   | 1                            | 0    | 0    | 0    |  |

| + 4.5 clock period shift        | 0    | 1   | 0                            | 0   | 1                            | 0    | 0    | 1    |  |

Figure 2. Examples for Input Offset Delay Timing

#### JTAG SUPPORT

The IDT72V70840 JTAG interface conforms to the Boundary-Scan standard IEEE-1149.1. This standard specifies a design-for-testability technique called Boundary-Scan test (BST). The operation of the boundary-scan circuitry is controlled by an external test access port (TAP) Controller.

#### TEST ACCESS PORT (TAP)

The Test Access Port (TAP) provides access to the test functions of the IDT72V70840. It consists of three input pins and one output pin.

Test Clock Input (TCK)

TCK provides the clock for the test logic. The TCK does not interfere with any on-chip clock and thus remain independent. The TCK permits shifting of test data into or out of the Boundary-Scan register cells concurrently with the operation of the device and without interfering with the on-chip logic.

Test Mode Select Input (TMS)

The logic signals received at the TMS input are interpreted by the TAP Controller to control the test operations. The TMS signals are sampled at the rising edge of the TCK pulse. This pin is internally pulled to Vcc when it is not driven from an external source.

Test Data Input (TDI)

Serial input data applied to this port is fed either into the instruction register or into a test data register, depending on the sequence previously applied to the TMS input. Both registers are described in a subsequent section. The received input data is sampled at the rising edge of TCK pulses. This pin is internally pulled to Vcc when it is not driven from an external source.

Test Data Output (TDO)

Depending on the sequence previously applied to the TMS input, the contents of either the instruction register or data register are serially shifted out towards the TDO. The data out of the TDO is clocked on the falling edge of the TCK pulses. When no data is shifted through the boundary scancells, the TDO driver is set to a high impedance state.

Test Reset (TRST)

Reset the JTAG scan structure. This pin is internally pulled to Vcc.

#### **INSTRUCTION REGISTER**

In accordance with the IEEE-1149.1 standard, the IDT72V70840 uses public instructions. The IDT72V70840 JTAG Interface contains a two-bit instruction register. Instructions are serially loaded into the instruction register from the TDI when the TAP Controller is in its shifted-IR state. Subsequently, the instructions are decoded to achieve two basic functions: to select the test data register that may operate while the instruction is current, and to define the serial test data register path, which is used to shift data between TDI and TDO during data register scanning. See Table below for Instruction decoding.

| Value | Instruction    | ion Function                  |  |  |  |  |  |  |

|-------|----------------|-------------------------------|--|--|--|--|--|--|

| 11    | Bypass         | Select Bypass Register        |  |  |  |  |  |  |

| 10    | Sample/Preload | Select Boundary Scan Register |  |  |  |  |  |  |

| 01    | Sample/Preload | Select Boundary Scan Register |  |  |  |  |  |  |

| 00    | EXTEST         | Select Boundary Scan Register |  |  |  |  |  |  |

JTAG Instruction Register Decoding

#### **TEST DATA REGISTER**

As specified in IEEE-1149.1, the IDT72V70840 JTAG Interface contains two test data registers:

The Boundary-Scan register

The Boundary-Scan register consists of a series of Boundary-Scan cells arranged to form a scan path around the boundary of the IDT72V70840 core logic.

The Bypass Register

The Bypass register is a single stage shift register that provides a one-bit path from TDI to its TDO. The IDT72V70840 boundary scan register bits are shown in Table 10. Bit 0 is the first bit clocked out. All three-state enable bits are active high.

## **TABLE 10 — BOUNDARY SCAN REGISTER BITS**

|            | Boundary Scan Bit 0 to bit 167 |                                       |           |  |  |  |  |  |  |

|------------|--------------------------------|---------------------------------------|-----------|--|--|--|--|--|--|

| Device Pin | Three-State                    | Output                                | Input     |  |  |  |  |  |  |

|            | Control                        | Scan Cell                             | Scan Cell |  |  |  |  |  |  |

| ODE        |                                |                                       | 0         |  |  |  |  |  |  |

| RESET      |                                |                                       | 1         |  |  |  |  |  |  |

| CLK        |                                |                                       | 2         |  |  |  |  |  |  |

| F0i        |                                |                                       | 3         |  |  |  |  |  |  |

| FE/HCLK    |                                |                                       | 4         |  |  |  |  |  |  |

| WFPS       |                                |                                       | 5         |  |  |  |  |  |  |

| DS         |                                |                                       | 6         |  |  |  |  |  |  |

| CS         |                                |                                       | 7         |  |  |  |  |  |  |

| R/W        |                                |                                       | 8         |  |  |  |  |  |  |

| AO         |                                |                                       | 9         |  |  |  |  |  |  |

| A1         |                                |                                       | 10        |  |  |  |  |  |  |

| A1<br>A2   |                                |                                       | 11        |  |  |  |  |  |  |

| A2<br>A3   |                                |                                       | 12        |  |  |  |  |  |  |

| A3<br>A4   |                                |                                       | 13        |  |  |  |  |  |  |

| A4<br>A5   |                                |                                       | 13        |  |  |  |  |  |  |

|            |                                |                                       |           |  |  |  |  |  |  |

| A6         |                                |                                       | 15        |  |  |  |  |  |  |

| A7         |                                |                                       | 16        |  |  |  |  |  |  |

| A8         |                                |                                       | 17        |  |  |  |  |  |  |

| A9         |                                |                                       | 18        |  |  |  |  |  |  |

| A10        |                                |                                       | 19        |  |  |  |  |  |  |

| A11        |                                |                                       | 20        |  |  |  |  |  |  |

| A12        |                                |                                       | 21        |  |  |  |  |  |  |

| <u>A13</u> |                                |                                       | 22        |  |  |  |  |  |  |

| DTA        |                                | 23                                    |           |  |  |  |  |  |  |

| D15        | 24                             | 25                                    | 26        |  |  |  |  |  |  |

| D14        | 27                             | 28                                    | 29        |  |  |  |  |  |  |

| D13        | 30                             | 31                                    | 32        |  |  |  |  |  |  |

| D12        | 33                             | 34                                    | 35        |  |  |  |  |  |  |

| D11        | 36                             | 37                                    | 38        |  |  |  |  |  |  |

| D10        | 39                             | 40                                    | 41        |  |  |  |  |  |  |

| D9         | 42                             | 43                                    | 44        |  |  |  |  |  |  |

| D8         | 45                             | 46                                    | 47        |  |  |  |  |  |  |

| D7         | 48                             | 49                                    | 50        |  |  |  |  |  |  |

| D6         | 51                             | 52                                    | 53        |  |  |  |  |  |  |

| D5         | 54                             | 55                                    | 56        |  |  |  |  |  |  |

| D4         | 57                             | 58                                    | 59        |  |  |  |  |  |  |

| D3         | 60                             | 61                                    | 62        |  |  |  |  |  |  |

| D2         | 63                             | 64                                    | 65        |  |  |  |  |  |  |

| D1         | 66                             | 67                                    | 68        |  |  |  |  |  |  |

| D0         | 69                             | 70                                    | 71        |  |  |  |  |  |  |

| TX31       | 72                             | 73                                    |           |  |  |  |  |  |  |

| TX30       | 74                             | 75                                    |           |  |  |  |  |  |  |

| TX29       | 76                             | 77                                    |           |  |  |  |  |  |  |

| TX28       | 78                             | 79                                    |           |  |  |  |  |  |  |

| TX27       | 80                             | 81                                    |           |  |  |  |  |  |  |

| TX26       | 82                             | 83                                    |           |  |  |  |  |  |  |

| TX25       | 84                             | 85                                    |           |  |  |  |  |  |  |

| TX24       | 86                             | 87                                    |           |  |  |  |  |  |  |

| RX31       |                                | , , , , , , , , , , , , , , , , , , , | 88        |  |  |  |  |  |  |

| RX30       |                                |                                       | 89        |  |  |  |  |  |  |

| RX29       |                                |                                       | 90        |  |  |  |  |  |  |

| RX29       |                                |                                       | 91        |  |  |  |  |  |  |

|            |                                |                                       | 71        |  |  |  |  |  |  |

|              | ı                      |                     |                    |

|--------------|------------------------|---------------------|--------------------|

|              |                        | ary Scan Bit 0 to   | bit 167            |

| Device Pin   | Three-State<br>Control | Output<br>Scan Cell | Input<br>Scan Cell |

| RX27         |                        |                     | 92                 |

| RX26         |                        |                     | 93                 |

| RX25         |                        |                     | 94                 |

| RX24         |                        |                     | 95                 |

| TX23         | 96                     | 97                  |                    |

| TX22         | 98                     | 99                  |                    |

| TX21<br>TX20 | 100<br>102             | 101<br>103          |                    |

| TX19         | 102                    | 105                 |                    |

| TX18         | 104                    | 103                 |                    |

| TX17         | 108                    | 107                 |                    |

| TX16         | 110                    | 111                 |                    |

| RX23         |                        |                     | 112                |

| RX22         |                        |                     | 113                |

| RX21         |                        |                     | 114                |

| RX20         |                        |                     | 115                |

| RX19         |                        |                     | 116                |

| RX18         |                        |                     | 117                |

| RX17         |                        |                     | 118                |

| RX16         | 120                    | 121                 | 119                |

| TX15<br>TX14 | 120                    | 121                 |                    |

| TX14         | 124                    | 125                 |                    |

| TX13         | 126                    | 127                 |                    |

| TX11         | 128                    | 129                 |                    |

| TX10         | 130                    | 131                 |                    |

| TX9          | 132                    | 133                 |                    |

| TX8          | 134                    | 135                 |                    |

| RX15         |                        |                     | 136                |

| RX14         |                        |                     | 137                |

| RX13         |                        |                     | 138                |

| RX12         |                        |                     | 139                |

| RX11         |                        |                     | 140                |

| RX10<br>RX9  |                        |                     | 141<br>142         |

| RX8          |                        |                     | 143                |

| TX7          | 144                    | 145                 | 143                |

| TX6          | 146                    | 147                 |                    |

| TX5          | 148                    | 149                 |                    |

| TX4          | 150                    | 151                 |                    |

| TX3          | 152                    | 153                 |                    |

| TX2          | 154                    | 155                 |                    |

| TX1          | 156                    | 157                 |                    |

| TX0          | 158                    | 159                 | 4/0                |

| RX7          |                        |                     | 160                |

| RX6<br>RX5   |                        |                     | 161<br>162         |

| RX4          |                        |                     | 163                |

| RX3          |                        |                     | 164                |

| RX2          |                        |                     | 165                |

| RX1          |                        |                     | 166                |

| RX0          |                        |                     | 167                |

#### **APPLICATIONS**

#### **CREATING LARGE SWITCH MATRICES**

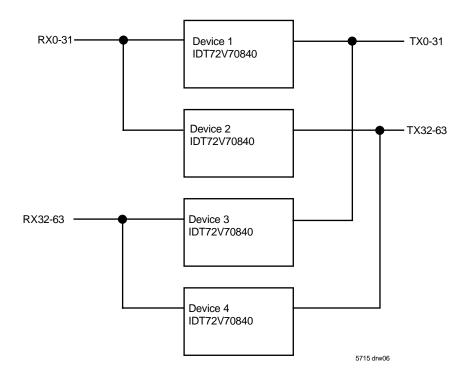

To create a switch matrix with twice the capacity of a given TSIS device, four devices must be used. In the example below, four IDT72V70840, 4096 x 4096 channel capacity devices are used to create an 8192 x 8192 channel switch matrix.

As can be seen, Device #1 and Device #2 will receive the same incoming RXO-31 data and thus have the same contents in Data Memory. On the output

side, however Device #1 is used to switch data out on to TX0-31 where as Device #2 is used to switch out on TX32-63. Like wise Device #3 and Device #4 are used in the same way as Device #1 and Device #2 but switch RX32-63, to TX0-31 and TX32-63. With this configuration all possible combinations of input and output streams are possible. In short, Device #1 is used to switch RX0-31 to TX0-31, Device #2 to switch RX0-31 to TX32-63, Device #3 to switch RX32-63 to TX0-31, and Device #4 to switch RX32-63 to TX32-63.

Figure 3. Creating Larger Switch Matrices

#### **ABSOLUTE MAXIMUM RATINGS**(1)

| Symbol | Parameter                  | Min.     | Max. | Unit |

|--------|----------------------------|----------|------|------|

| Vcc    | Supply Voltage             | 3.0      | 3.6  | V    |

| Vi     | Voltage on Digital Inputs  | GND -0.3 | 5.3  | ٧    |

| lo     | Current at Digital Outputs | -50      | 50   | mA   |

| Ts     | Storage Temperature        | -55      | +125 | °C   |

| PD     | Package Power Dissapation  |          | 2    | W    |

#### NOTE:

## RECOMMENDED OPERATING CONDITIONS<sup>(1)</sup>

| Symbol | Parameter                          | Min. | Тур. | Max. | Unit |

|--------|------------------------------------|------|------|------|------|

| Vcc    | Positive Supply                    | 3.0  | 3.3  | 3.6  | ٧    |

| VIH    | Input HIGH Voltage                 | 2.0  |      | 5.3  | ٧    |

| VIL    | Input LOW Voltage                  | _    |      | 0.8  | ٧    |

| Тор    | OperatingTemperature<br>Commercial | -40  | 25   | +85  | °C   |

#### NOTE:

1. Voltages are with respect to Ground unless otherwise stated.

#### DC ELECTRICAL CHARACTERISTICS

| Symbol               | Parameter                   | Min. | Тур. | Max. | Units |

|----------------------|-----------------------------|------|------|------|-------|

| Icc (2)              | Supply Current @ 2.048 Mb/s | -    | 15   | 20   | mA    |

|                      | @ 4.096 Mb/s                | -    | 25   | 35   | mA    |

|                      | @ 8.192 Mb/s                | -    | 47   | 70   | mA    |

| IIL <sup>(3,4)</sup> | Input Leakage (input pins)  | -    | -    | 50   | μΑ    |

| loz <sup>(3,4)</sup> | High-impedance Leakage      | -    | -    | 50   | μΑ    |

| VoH <sup>(5)</sup>   | Output HIGH Voltage         | 2.4  | -    | •    | V     |

| VoL <sup>(6)</sup>   | Output LOW Voltage          | -    | -    | 0.4  | V     |

#### NOTES:

- 1. Voltages are with respect to ground (GND) unless otherwise stated.

- 2. Outputs unloaded.

- 3.  $0 \le V \le VCC$ .

- 4. Maximum leakage on pins (output or I/O pins in high-impedance state) is over an applied voltage (V).

- 5. IOH = 10 mA.

- 6. IOL = 10 mA.

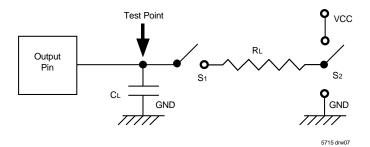

## AC ELECTRICAL CHARACTERISTICS - TIMING PARAMETER MEASUREMENT VOLTAGE LEVELS

| Symbol | Rating                               | Level | Unit |

|--------|--------------------------------------|-------|------|

| VTT    | TTLThreshold                         | 1.5   | ٧    |

| VHM    | TTL Rise/Fall Threshold Voltage HIGH | 2.0   | ٧    |

| VLM    | TTL Rise/Fall Threshold Voltage LOW  | 8.0   | V    |

Figure 4. Output Load

S1 is open circuit except when testing output levels or high impedance states.

S2 is switched to Vcc or GND when testing output levels or high impedance states.

Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

## **AC ELECTRICAL CHARACTERISTICS - FRAME PULSE AND CLK**

| Symbol               | Parameter                                                                              | Min.             | Тур.             | Max.             | Units          |

|----------------------|----------------------------------------------------------------------------------------|------------------|------------------|------------------|----------------|

| tfpw <sup>(1)</sup>  | Frame Pulse Width (ST-BUS®, GCI) Bit rate = 2.048 Mb/s Bit rate = 4.096 Mb/s           | 26<br>26         |                  | 295<br>145       | ns<br>ns       |

|                      | Bit rate = 8.192 Mb/s                                                                  | 26               | _                | 80               | ns             |